La hòstia de silicona sobre aïllants (SOI) de Semicera està a l'avantguarda de la innovació de semiconductors, oferint un aïllament elèctric millorat i un rendiment tèrmic superior. L'estructura SOI, que consisteix en una fina capa de silici sobre un substrat aïllant, proporciona avantatges crítics per als dispositius electrònics d'alt rendiment.

Les nostres hòsties SOI estan dissenyades per minimitzar la capacitat parasitària i els corrents de fuga, la qual cosa és essencial per desenvolupar circuits integrats d'alta velocitat i baixa potència. Aquesta tecnologia avançada garanteix que els dispositius funcionin de manera més eficient, amb una velocitat millorada i un consum d'energia reduït, crucial per a l'electrònica moderna.

Els processos de fabricació avançats emprats per Semicera garanteixen la producció d'hòsties SOI amb una excel·lent uniformitat i consistència. Aquesta qualitat és vital per a aplicacions en telecomunicacions, automoció i electrònica de consum, on es requereixen components fiables i d'alt rendiment.

A més dels seus avantatges elèctrics, les hòsties SOI de Semicera ofereixen un aïllament tèrmic superior, millorant la dissipació de calor i l'estabilitat en dispositius d'alta densitat i alta potència. Aquesta característica és especialment valuosa en aplicacions que impliquen una generació de calor significativa i requereixen una gestió tèrmica eficaç.

En triar l'oblea aïllant de silicona de Semicera, invertiu en un producte que admeti l'avenç de les tecnologies d'avantguarda. El nostre compromís amb la qualitat i la innovació garanteix que les nostres hòsties SOI compleixin les rigoroses demandes de la indústria dels semiconductors actuals, proporcionant la base per als dispositius electrònics de nova generació.

| Elements | Producció | Recerca | Maniquí |

| Paràmetres de cristall | |||

| Politipus | 4H | ||

| Error d'orientació superficial | <11-20 >4±0,15° | ||

| Paràmetres elèctrics | |||

| Dopant | Nitrogen de tipus n | ||

| Resistivitat | 0,015-0,025 ohm·cm | ||

| Paràmetres mecànics | |||

| Diàmetre | 150,0 ± 0,2 mm | ||

| Gruix | 350±25 μm | ||

| Orientació plana primària | [1-100]±5° | ||

| Longitud plana primària | 47,5 ± 1,5 mm | ||

| Pis secundari | Cap | ||

| TTV | ≤5 μm | ≤10 μm | ≤15 μm |

| LTV | ≤3 μm (5mm * 5mm) | ≤5 μm (5mm * 5mm) | ≤10 μm (5 mm * 5 mm) |

| Arc | -15μm ~ 15μm | -35μm ~ 35μm | -45μm ~ 45μm |

| Deformació | ≤35 μm | ≤45 μm | ≤55 μm |

| Rugositat frontal (Si-face) (AFM) | Ra≤0,2 nm (5 μm * 5 μm) | ||

| Estructura | |||

| Densitat de microtubes | <1 ea/cm2 | <10 ea/cm2 | <15 ea/cm2 |

| Impureses metàl·liques | ≤5E10àtoms/cm2 | NA | |

| BPD | ≤1500 ea/cm2 | ≤3000 ea/cm2 | NA |

| TSD | ≤500 ua/cm2 | ≤1000 ea/cm2 | NA |

| Qualitat frontal | |||

| Davant | Si | ||

| Acabat superficial | Si-face CMP | ||

| Partícules | ≤60ea/hòstia (mida ≥0,3μm) | NA | |

| Esgarrapades | ≤5ea/mm. Longitud acumulada ≤Diàmetre | Longitud acumulada ≤ 2 * Diàmetre | NA |

| Pela de taronja/foses/taques/estries/esquerdes/contaminació | Cap | NA | |

| Estelles de vora/sagnies/fractura/plaques hexagonals | Cap | ||

| Zones politipus | Cap | Àrea acumulada ≤20% | Àrea acumulada ≤30% |

| Marcatge làser frontal | Cap | ||

| Tornar Qualitat | |||

| Acabat posterior | CMP cara C | ||

| Esgarrapades | ≤5ea/mm, longitud acumulada≤2 * Diàmetre | NA | |

| Defectes posteriors (estelles de vora/sagnies) | Cap | ||

| Rugositat de l'esquena | Ra≤0,2 nm (5 μm * 5 μm) | ||

| Marcatge làser posterior | 1 mm (des de la vora superior) | ||

| Edge | |||

| Edge | Xamfrà | ||

| Embalatge | |||

| Embalatge | Epi-ready amb envasat al buit Embalatge de casset multiwafer | ||

| *Notes: "NA" significa que no hi ha cap sol·licitud. Els elements no esmentats poden referir-se a SEMI-STD. | |||

-

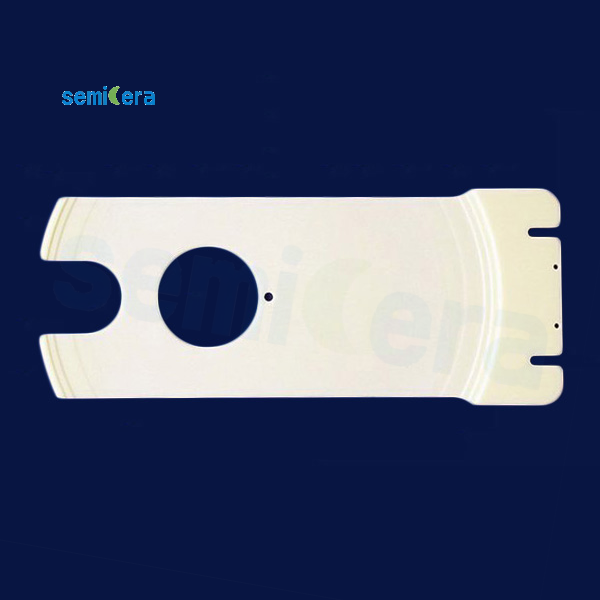

Forquilla de ceràmica semiconductora de zirconi

-

Susceptor d'hòsties de grafit de recobriment de SiC

-

Vaixell d'hòstia de carbur de silici de grau superior per a cr...

-

Vaixell d'hòsties de carbur de silici

-

Forn de buit Escalfador elèctric de grafit personalitzat

-

Susceptor de barril recobert de carbur de silici